Find the best fit for your network needs

share:

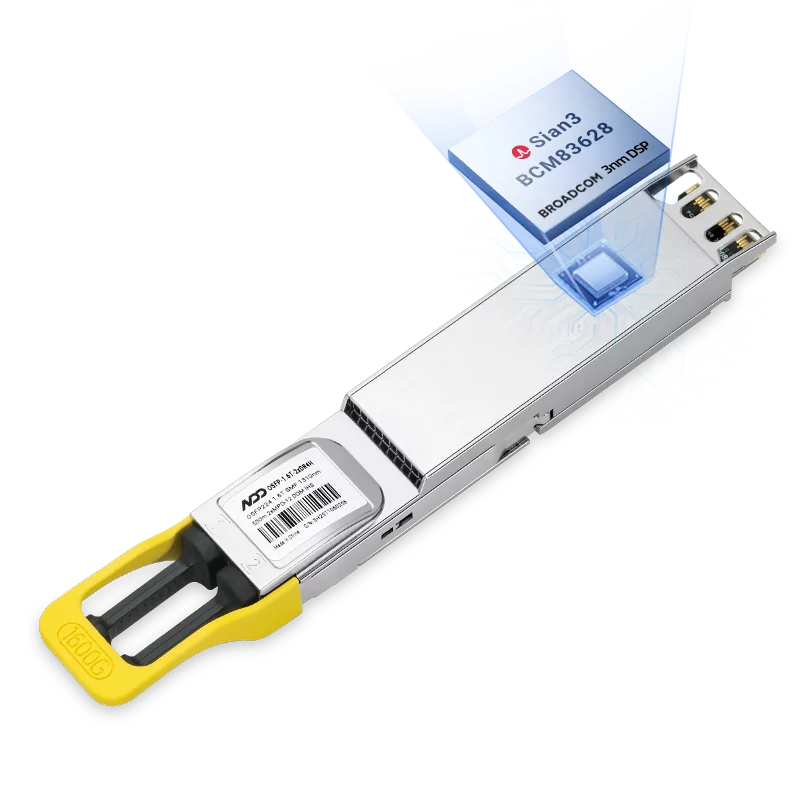

800GBASE-2xSR4 OSFP PAM4 850nm 50m MMF Module

800GBASE-2xSR4 OSFP PAM4 850nm 50m MMF ModuleLearn More

Popular

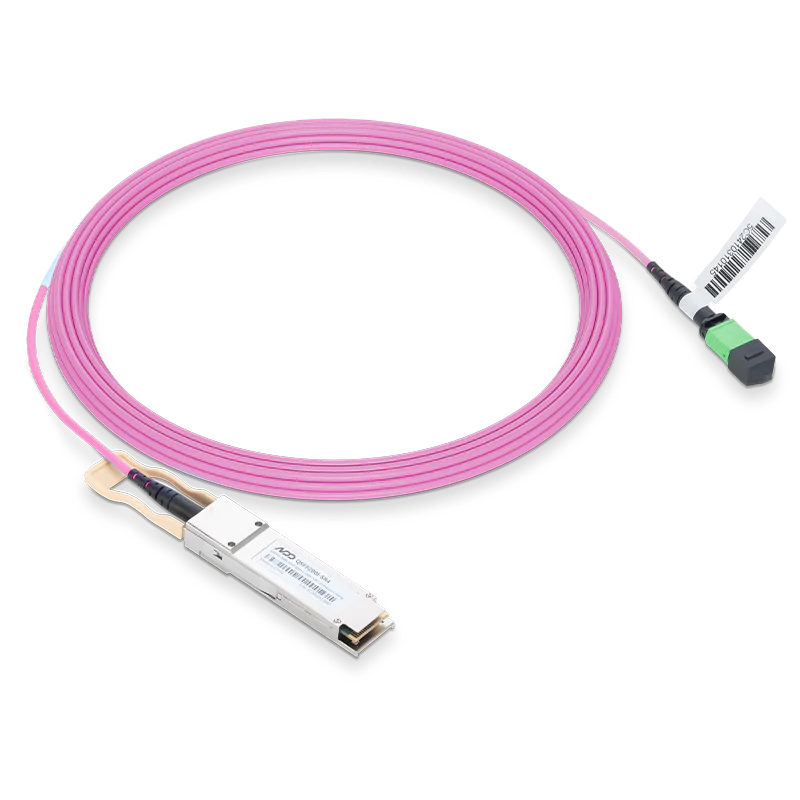

- 1Active Optical Cable Jacket Explained: OFNR vs OFNP vs PVC vs LSZH?

- 2Perfect Solution for 25G Bidirectional ER 40km: 25G BiDi 1289nm/1314nm

- 3How to Choose the Right Cat6a Cable for 10G Networks

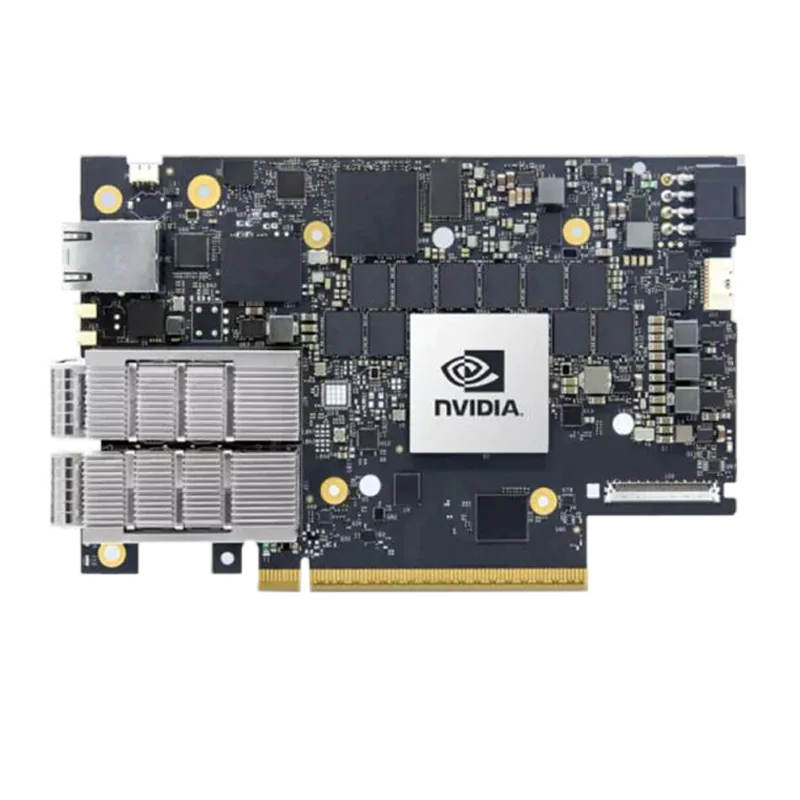

- 4The Key Role of High-quality Optical Transceivers in AI Networks

- 5Common Problems While Using Optical Transceivers in AI Clusters